# Empowering Innovation in Logic Verification

Harnessing collective wisdom across tools, processes, and people

## Chilai Huang

Senior Director of R&D for Verification IP Digital Verification Technologies

## **Gordon Allan**

Product Manager for Verification IP Digital Verification Technologies

SIEMENS

Unrestricted | © Siemens 2024 | Siemens Digital Industries Software

Artificial Intelligence is not an end in itself but a means to achieve transformative solutions for realworld challenges.

## Total Semiconductor Market and AI Semiconductor Market

In 2023 21% of semiconductor market associated with AI and grows to 73% by 2030

Source: IBS Jan 2024 Report: First Generative AI Report: Impact of Generative AI on Semiconductor Industry

Page 3 Unrestricted | © Siemens 2024 | Siemens Digital Industries Software

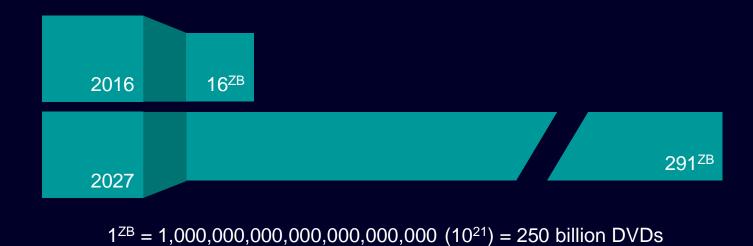

## Disruptive trends in the global datasphere

Reshaping computing, networking, communication, security, and applications

Global Datasphere is a measure of how much data is created, captured, replicated, and consumed each year.

Source: IDC Apr 2023 Report: Worldwide IDC Global Datasphere Forecast, 2023-2027

Page 4 Unrestricted | © Siemens 2024 | Siemens Digital Industries Software

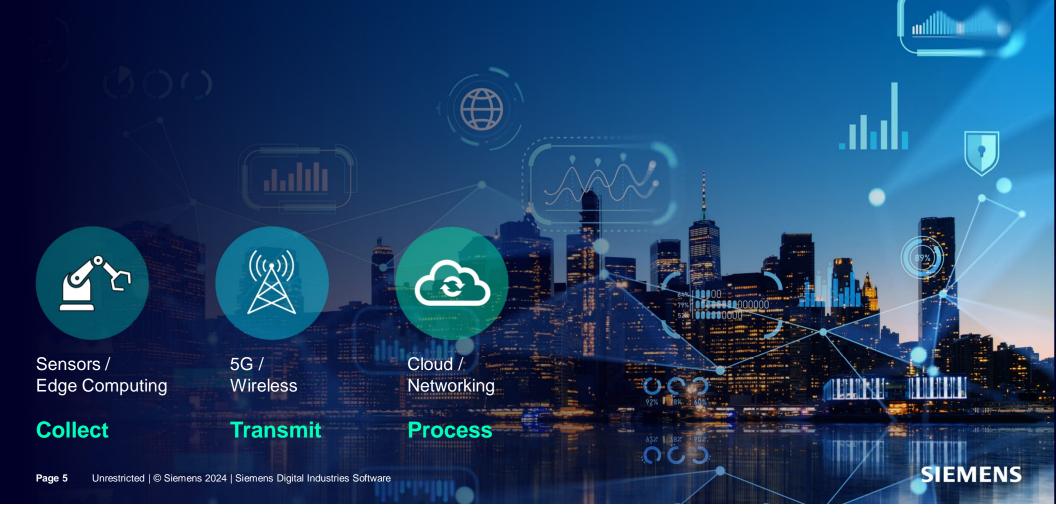

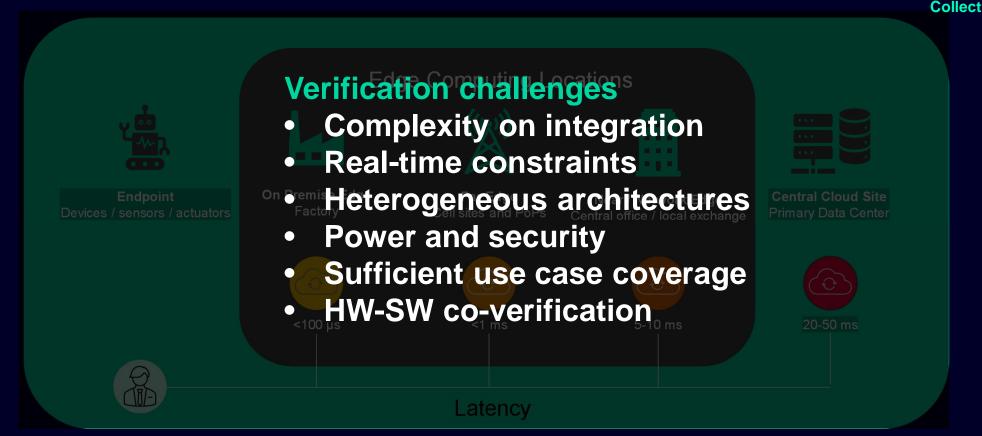

Macro trends in growing complexity Reshaping computing, networking, communication, security, and applications

Edge computing trends — it's all about latency! 75% of data compute moves to the edge in the next few years

Source: Application PerformancemArticles, Digital Experience, Network Performance, Mar 24, 2022 AXIOS, AI drives explosion in edge computing, Feb 16, 2024

Page 6 Unrestricted | © Siemens 2024 | Siemens Digital Industries Software

#### Hyperconnected world by 2030

44 billion devices connected to the internet by 2030, growing at a 12% CAGR

( ( ) )

Hyperscale computing — it's all about scalability! Cost-effectiveness, high performance, reliability and resilience, support big data

**Hyperscale Servers** A substantial \$187B, making up 63% of the total investment.

A constant of the second state of the second s

\$4B, accounting for 1% the total investment.

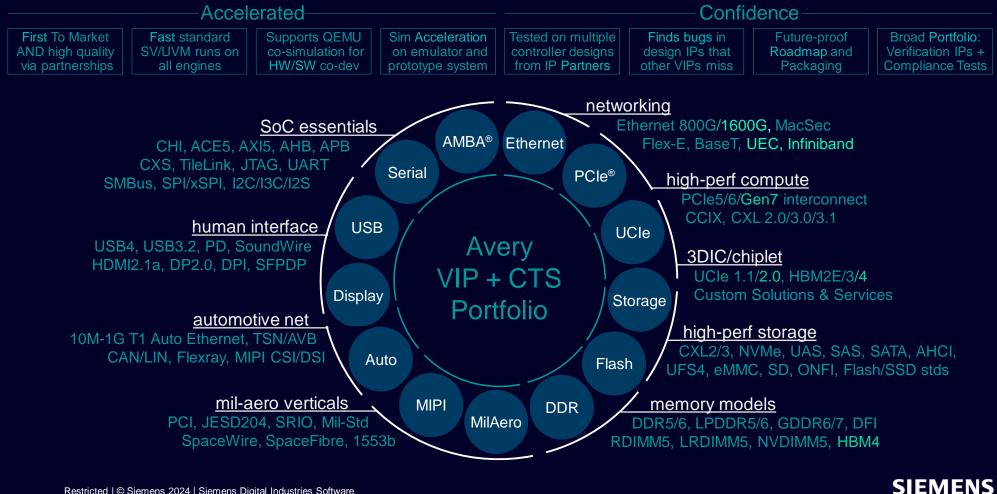

## Accelerated Confidence from Siemens EDA – Avery Verification IP broad portfolio

Restricted | © Siemens 2024 | Siemens Digital Industries Software

## Accelerated Confidence from Siemens EDA – Avery Compliance Test Suites find bugs!

| Accelerated      |                |                   |                  | Confidence         |                 |              |                    |

|------------------|----------------|-------------------|------------------|--------------------|-----------------|--------------|--------------------|

| First To Market  | Fast standard  | Supports QEMU     | Sim Acceleration | Tested on multiple | Finds bugs in   | Future-proof | Broad Portfolio:   |

| AND high quality | SV/UVM runs on | co-simulation for | on emulator and  | controller designs | design IPs that | Roadmap and  | Verification IPs + |

| via partnerships | all engines    | HW/SW co-dev      | prototype system | from IP Partners   | other VIPs miss | Packaging    | Compliance Tests   |

#### Build vs Buy? Rely on Avery VIP+CTS for compliance/quality, freeing up your resources

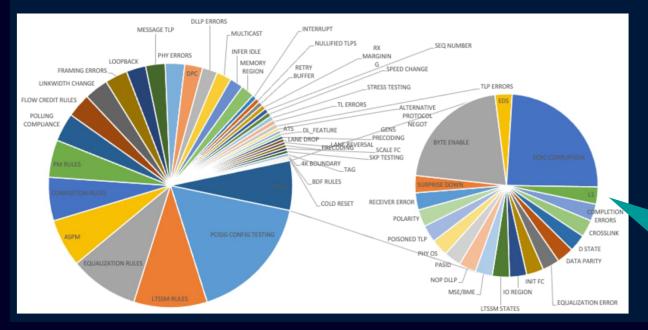

#### **Avery Compliance Test Suites:**

- Covers whole spec, not just std tests

- Constrained-random SV/UVM code

- Full test plan and coverage model

- Still finding PCIe5 bugs in IP configs

- The industry's signoff VIP / test suite

"you found an IP bug the IP vendor VIP did not catch – with just ONE test" – HPC customer

Restricted | © Siemens 2024 | Siemens Digital Industries Software

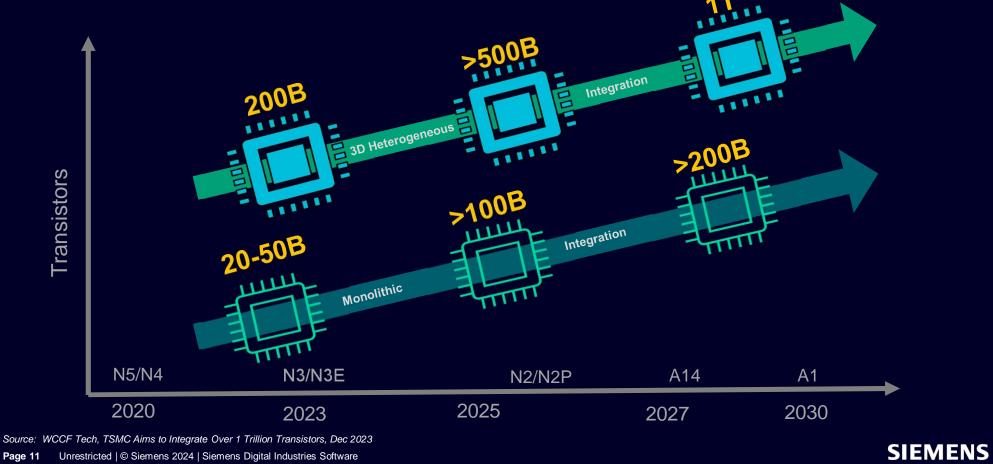

**Chiplets and 3DIC** Moving monolithic SoCs to 3DIC and chiplet-based design

Unrestricted | © Siemens 2024 | Siemens Digital Industries Software Page 11

## **Chiplets and 3DIC**

Moving monolithic SoCs to 3DIC and chiplet-based design

#### **Cost-effective scaling**

Alternative to traditional Moore's Law scaling through higher integration

#### **Enhanced performance**

Increases processing power and speed by reducing interconnect

#### **Reduce power consumption**

Shorter interconnects reduce power loss and improve energy efficiency

#### Interconnect protocol challenges

- Verifying that complex interconnect protocols adhere to specification

- Verifying compatibility between different chiplets from various vendors or design team

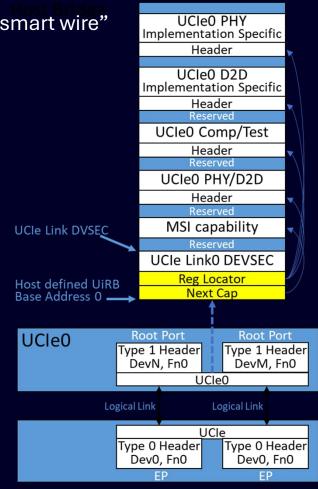

#### Why do we need UCIe and how do we deal with that complexity? Moving from a simple "wire" to a complex managed die-to-die protocol "smart wire"

Building a standards-based chiplet ecosystem:

Flexible: Highly configurable Interconnect

• package, modules, protocols, flits modes

Native: built-in support for PCIe/CXL flit format

leveraging PCIe/CXL software stack

Inclusive: other protocols over streaming mode

• Example: AXI, CHI, CXS

**Expandable: retimer support**

Enable off-package electrical/optical link

#### UCle comes of age with the UCle 2.0 specification (August 2024) Adds manageability architecture, debug and test support, sideband extensions, 3D PHY

**UCIe Manageability Architecture**

- Management Transport Protocols

- UCIe Memory Access Protocol (UMAP)

- UCle Test and Debug Protocol

- Vendor Defined Protocol

- Management Transport Packet

- Management Capability Structure

- UCle Debug and Test (DFx) Architecture

- Utilizes Manageability Infrastructure

- X8 Standard Package Support

Sideband Feature Extensions (SBFE)

- Sideband-only (SO) Port

- Sideband Performant Mode Operation (PMO) UCle-3D PHY

Our statement of support in the UCle2.0 launch on Aug 6 2024: "Building on our leadership in chiplets technology and .... With our UCle2.0 Verification IP and Compliance Test Suite solutions, Siemens continues its UCle design verification leadership.

And because version 2.0 of the UCIe standard incorporates advances that support mainstream design for test (DFT) practices, it paves the way for nextgeneration products capable of fully leveraging Siemens' industry-leading Tessent software." Mike Ellow, CEO of Silicon Systems for Siemens EDA

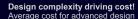

**Software defines and differentiates successful products** Development & validation must start as early as possible

Software Key Component of Chip Architecture

- Increasing transistor count

- Rise in workload-optimized chips

- High mask and fab costs; first silicon success is crucial

#### **Software Dominates Costs**

- Software is a key differentiator

- Delays in software readiness are costly

- Essential for silicon sales

#### Page 15 Unrestricted | © Siemens 2024 | Siemens Digital Industries Software

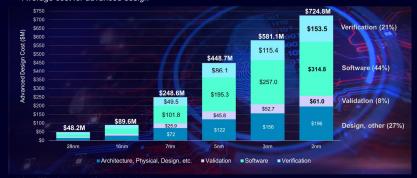

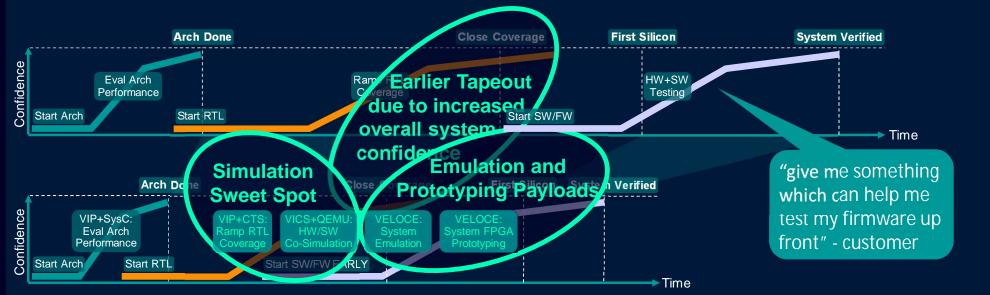

## Accelerated Confidence from Siemens EDA – Software stimulus and early FW dev

Virtual In-Circuit Simulation + QEMU - seamless shift from Sequences to Software, Accelerate HW/SW signoff

Restricted | © Siemens 2024 | Siemens Digital Industries Software

Restricted | © Siemens 2024 | Siemens Digital Industries Software

## What EDA is doing to help? proFPGA prototyping plus Avery Speed Adapters

#### Advanced protocol Speed Adapters quality

- Veloce proFPGA is the prototyping reference platform for validation

- Guarantees quality, performance and full compatibility

- Easy access to proFPGA prototyping HW & SW platform

- proFPGA modularity and flexibility allows to mimic customers' proFPGA setup

- Large set of extension boards available with proFPGA

- Automated, timing driven VPS user' software flow to synthesize and compile the design

#### Consolidated roadmap and vision for the future

- Timely availability of protocol speed adapters with proFPGA

- Alignment to customers' requirements: platform, extension boards and protocols

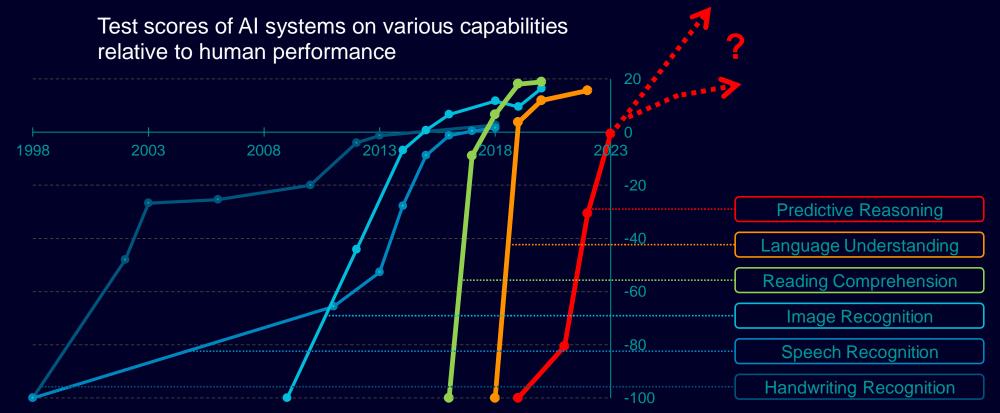

## Huge AI chip design growth – Why now?

Data Source: Kiela et al. (2023) - with minor processing by Our World in Data

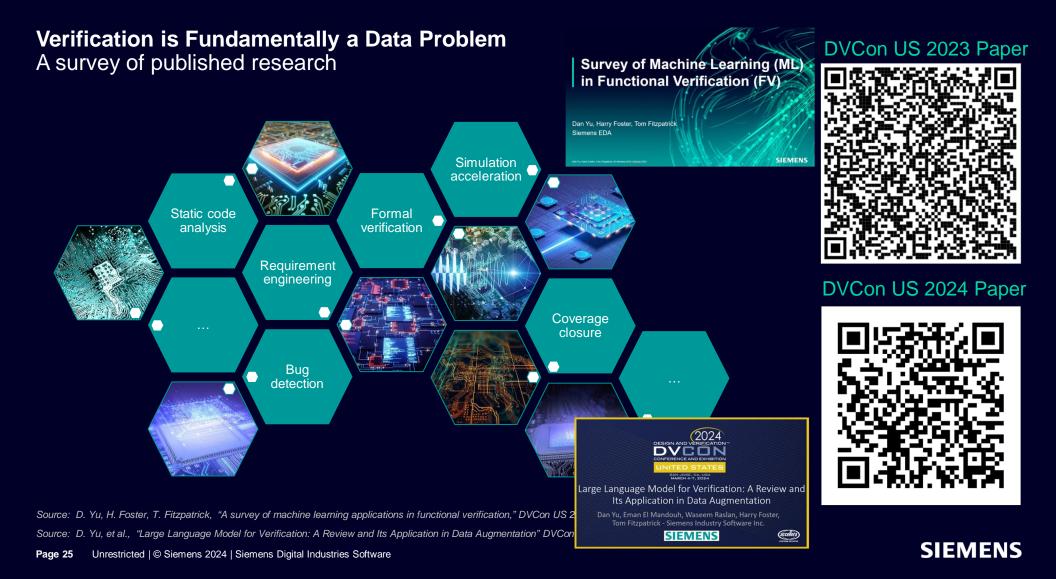

What EDA is doing to help? Siemens Approach to Data and ML Innovation Building on the strength of the larger Siemens organization

Collaboration

## What EDA is doing to help? Investing in future AI scale-up and scale-out Protocols

#### Some protocol examples:

#### NVIDIA NVLink and NVLink-C2C

NVIDIA solutions for scaling IO within server

- Enable high-speed, collective operations

- C2C Supports CHI and CXL layers

- Opportunity for custom VIP / partnership

- Opportunity for expert services business

#### Infiniband

Legacy high performance network solution

- Competing with multi-GB ethernet

- Less well served with Verification IP

- Customer interest continues

- Need more industry / partner data

#### Ultra Ethernet (UEC/UET)

Keeping up with throughput and latency needs of AI clusters Ultra Ethernet Transport (UET) replaces RoCE, provides:

- Multipath, packet spraying, flexible delivery order, new congestion control, telemetry, efficient security built-in

- Larger scale, stability, and reliability

#### Ultra Accelerator Link (UALink)

Scale-up connect between AI accelerators and switches: Open Industry Standard Interface for Enabling Highperformance, Low-latency Communications Interconnect for Next-generation AI Accelerators in Data Centers Newly forming consortium

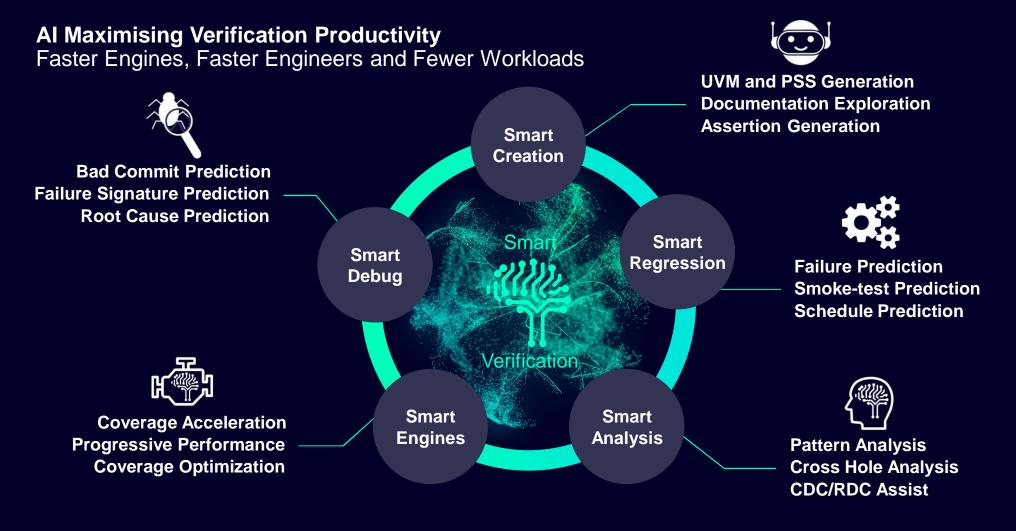

## **Questa AI Powered Smart Verification**

| Product                  | Technology                       | AI Value Observed                                                                  |                                    |  |  |

|--------------------------|----------------------------------|------------------------------------------------------------------------------------|------------------------------------|--|--|

| VIQ Coverage<br>Analyzer | Pattern & Cross Hole<br>Analysis | <b>3x</b> reduction in coverage closure time                                       | Smart<br>Creation                  |  |  |

| CDC/RDC                  | CDC/RDC Assist                   | <b>90%</b> reduction in crossing violations                                        |                                    |  |  |

| VIQ<br>Regression IQ     | Failure Prediction               | <b>100x</b> faster to find first failure and <b>2x</b> faster to find last failure | Smart<br>Debug                     |  |  |

|                          | Smoke Test Prediction            | <b>10x</b> reduction in smoke test regression time                                 | Verification                       |  |  |

| VIQ<br>Debug IQ          | Bad Commit Prediction            | <b>2x</b> reduction to find and confirm bad check-<br>ins                          | Smart<br>Engines Smart<br>Analysis |  |  |

|                          | Signature Prediction             | <b>30%</b> reduction in overall debug time                                         |                                    |  |  |

| Questa Sim               | Coverage Acceleration            | <b>100x</b> faster time to coverage closure with <b>500x</b> fewer tests           |                                    |  |  |

#### Summary

Harnessing Collective Wisdom Across Tools, Processes, and People

#### Al is a means to achieve transformation, not an end in itself

- Natural language is not suitable for complex design description

- Generative model need to be enhanced to handle long sequences and relationship of those tokens

- Specific agents should be built to have domain specific knowledges

#### **Macro Trends**

- Semiconductor transformation

- Data explosion changing everything

- Movement to Software Defined Products

- Decline in engineering talent demands smarter verification

- Sustainable solutions is no longer an option

## The need for Accelerated Confidence

• Complex 3DIC verification, enabling Software co-simulation, effective prototyping acceleration

## Contact

Published by Siemens DISW

Chilai Huang Senior Director, Siemens EDA Design Verification Technologies E-mail chilai.huang@siemens.com

Page 26 Unrestricted | © Siemens 2024 | Siemens Digital Industries Software