# Better Late Than Never Collecting Coverage from Zeroes and Ones

Rich Edelman, Siemens EDA, Fremont, CA US Tsung-Yu Tsai, Siemens Taiwan, HsinChu City, Taiwan

## Background

- Files of zeroes and ones

- ASCII expected and actual

- VCD

- qwave.db

- WLF

- other

- Coverage

- Toggle

- Block

- FSM

- Conditional

- Functional

| 10  | 10101010110011010101011001  |

|-----|-----------------------------|

| 20  | 00101010110100010101011010  |

| 30  | 10101010110111010101011011  |

| 40  | 00101010111000010101011100  |

| 50  | 10101010111011010101011101  |

| 60  | 00101010111100010101011110  |

| 70  | 101010101111110101010111111 |

| 80  | 00101010110000010101011000  |

| 90  | 10101010110011010101011001  |

| 100 | 00101010110100010101011010  |

#### Concept – Imagination

- Coverage wasn't modeled

- Management decision No time in the schedule maybe it is an FPGA

- But we'd like to know about some of the coverage

- Build a Verilog instance tree that has names like the real design

- This makes the coverage report easy to read

- At each instance, populate it with the "sampled value datatypes" (reg[3:0]valueB)

- Build a functional coverage model for the variables.

- coverpoint, bins, crosses

- Now, assign those zeroes and ones to the variables in turn. Collecting coverage

# Conceptual Flow

10 010101010110 20 101011101011

30 101010111111

40 000001110001

Simulation of coverage models

#### The File Reader

- A "global" variable to hold the line of bits

- Get the filename

- Open the file using \$fopen

```

module top();

// A "global" variable to hold the line

// JUST read. The DUT-coverage-model uses

// this to assign the parts.

bit [1023:0] vector;

initial begin

bit [1023:0] my values;

string filename;

longint my time, now;

int d;

integer fd, code;

now = 0;

if (!$value$plusargs("i=%s", filename))

filename = "testfile.txt";

$display("...processing '%s'", filename);

// Open the "values" file

fd = $fopen(filename, "r");

```

#### The File Reader

- Read the whole file

- Use \$fscanf

- Read the time

- Read the bit vector

- Update the current time

- Apply the bits to the "global" holding bit vector

```

// Loop through each line, one at a time.

// 1. Update the time

// 2. Apply the values

3. Repeat for each line

forever begin

// Read a line

code = $fscanf(fd, "%d %b", my time, my values);

if (code == -1) begin

$finish(2);

end

// Update time

d = my time - now;

#d;

now = now + d;

// Apply the values to the global

vector = my values;

end

end

endmodule

```

## Assigning the bits

```

module M();

ABC abc0();

ABC abc1();

// When the intermediate vector changes, assign

// its contents to the underlying values - deep

// in the hierarchy or on the top

always @(top.vector) begin

$display("@%t: Vector=%20b", $time, top.vector);

abc0.a.valueA, abc0.b.valueB, abc0.c.valueC,

abc1.a.valueA, abc1.b.valueB, abc1.c.valueC

} = top.vector;

end

endmodule

```

```

10101010110011010101011001

00101010110100010101011010

10101010110111010101011011

00101010111000010101011100

10101010111011010101011101

60 00101010111100010101011110

70 10101010111111010101011111

80 00101010110000010101011000

90 10101010110011010101011001

100 00101010110100010101011010

abc0.a.valueA[4:0],

abc0.b.valueB[4:0],

abc0.c.valueC[2:0]

abc1.a.valueA[4:0],

abc1.b.valueB[4:0],

abc1.c.valueC[2:0]

```

# A Simple Functional Coverage Model

- Construct a coverage object 'cgi'.

- Write a coverage model. Simple in this case.

- Inside the module A(), a value 'valueA'.

- valueA got assigned by the concatenation above.

- Once valueA changes, trigger a call to sample().

```

module A();

req [4:0] valueA;

covergroup cq;

cp valueA: coverpoint valueA;

endgroup

cg cgi = new();

always @ (valueA) begin

$display("@%t: %m.valueA=%20b",

$time, valueA);

cgi.sample();

end

endmodule

```

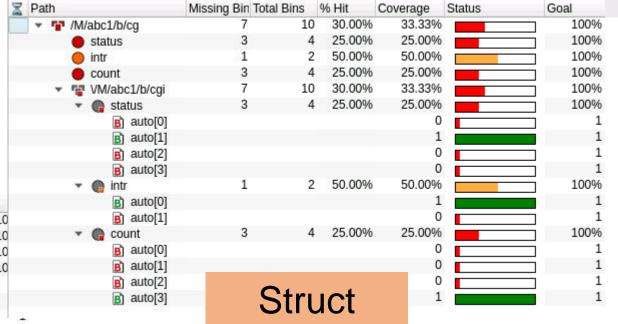

#### Structs too

- Exactly the same concepts.

- Assign, trigger, call sample()

```

module B();

reg [4:0] valueB;

covergroup cq;

cp valueB: coverpoint valueB;

endgroup

cq cqi = new();

always @ (valueB) begin

cgi.sample();

end

endmodule

```

```

module B();

typedef struct packed {

reg [1:0] status;

req intr;

reg [1:0] count;

} csr reg t;

csr reg t valueB;

covergroup cg;

status: coverpoint valueB.status;

intr: coverpoint valueB.intr;

count: coverpoint valueB.count;

endgroup

cq cqi = new();

always @ (valueB) begin

cgi.sample();

end

endmodule

```

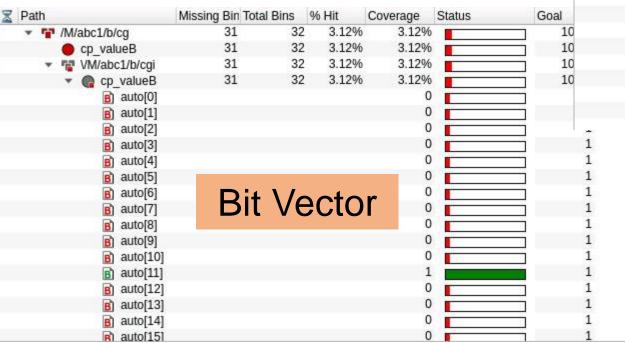

# Coverage

- Bit Vector model

- Struct model

- This is our "regular" model

- A value is going to be assigned as read from the file

- A covergroup was designed

- cgi.sample() is triggered

What other coverage can be collected?

```

module C();

reg [2:0] valueC;

covergroup cg;

cp_valueC: coverpoint valueC;

endgroup

cg cgi = new();

always @(valueC) begin

cgi.sample();

end

endmodule

```

## What about other kinds of coverage?

Write a "fake" FSM in the 'module C'

It gets recognized by the compiler / optimizer

- But it never operates the states are assigned

- Notice the 'fake\_clk"

- it doesn't run

```

module C();

reg [2:0] valueC;

reg clk, fake clk;

always @ (posedge fake clk) begin

case (valueC)

ZERO: valueC <= ONE;</pre>

ONE: valueC <= TWO;

TWO: valueC <= THREE;

THREE: valueC <= FOUR;

FOUR: valueC <= FIVE;

FIVE: valueC <= SIX;</pre>

SIX: valueC <= SEVEN;

SEVEN: valueC <= ZERO;

endcase

end

endmodule

```

- Since the state machine doesn't "run"

- Block / Statement coverage doesn't register

```

45

always @(posedge fake_clk) begin

46xa X=

case(valueC)

47x

ZERO: valueC <= ONE;

48x

ONE: valueC <= TWO;

49x

TWO: valueC <= THREE;

50x

THREE: valueC <= FOUR;

51x

FOUR: valueC <= FIVE;

52x

FIVE: valueC <= SIX;

53x

SIX: valueC <= SEVEN;

54x

SEVEN: valueC <= ZERO;

55

endcase

56

end

```

- 'valueC' is being assigned

- the state and transition coverage is collected

```

module C();

reg [2:0] valueC;

reg clk, fake clk;

always @ (posedge fake clk) begin

Count: 1

THREE/.

Count: 1

FOUR/1

Count: 1

FIVE/1

Count: 1

SIX/1

case(valueC)

ZERO: valueC <= ONE;</pre>

ONE: valueC <= TWO;

TWO: valueC <= THREE;

THREE: valueC <= FOUR;

FOUR: valueC <= FIVE;

FIVE: valueC <= SIX;

SIX: valueC <= SEVEN;

SEVEN: valueC <= ZERO;

endcase

end

endmodule

```

An always block that operates expressions but does NOT change the "values" that are assigned from the file

```

module C();

reg [2:0] valueC;

27

reg clk;

28

always begin

291

#1; clk = 0;

int count;

always @ (posedge clk) begin

30/

#1; clk = 1;

if (valueC == ONE) begin

31

end

32

always begin

count++;

33

always @(posedge clk) begin

#1; clk = 0;

end

344

if (valueC == ONE) begin

#1; clk = 1;

35

count++;

else if (valueC == TWO) begin

36

end

end

count--;

371

else if (valueC == TWO) begin

384

end

count --;

39

end

else

404

else

count = 13;

411

count = 13;

421

$display("@%t: %m.count=%d", $time, count);

end

43

end

```

The expressions and branches and lines can be covered — they are conditioned with 'valueC' from the file assigns

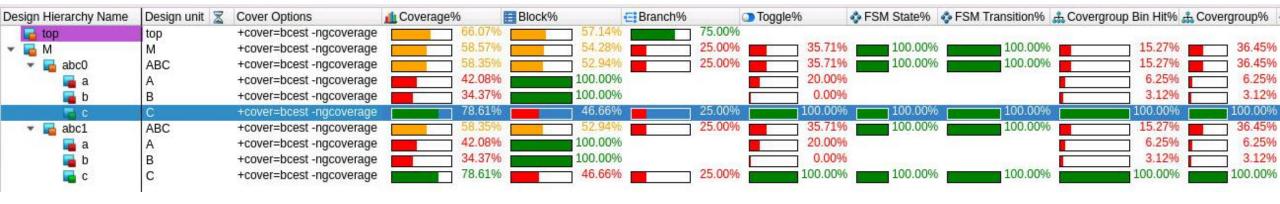

# Coverage Roll-up

- Not all the coverage categories are "valid"

- It "depends"

- Covergroups/Toggle/FSM all good

- Block/Branch depends on the module/instance

#### Conclusion

- Coverage is a useful tool for measuring "completeness"

- Even after the fact, a file of zeroes and ones can be used to collect coverage

- Have all the legal values been used

- Have all the legal "crosses" between two variables been used

- Building a small structure helps with naming conventions and reporting

- Keep the system simple

- Explore more kinds of coverage that might apply to this scheme

#### Questions

• Source code available – contact <u>rich.edelman@siemens.com</u>